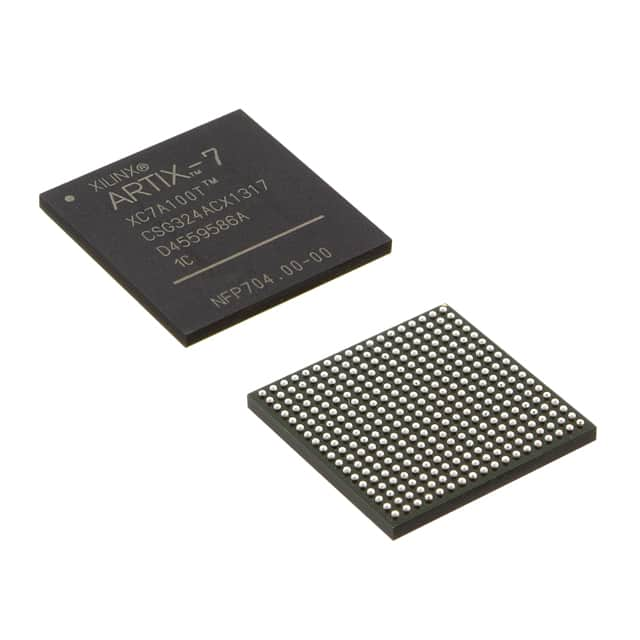

Orizjinele IC-chip Programmierber XCVU440-2FLGA2892I IC FPGA 1456 I/O 2892FCBGA

Produkt Attributen

| TYPE | BESKRIUWING |

| Kategory | Integrated Circuits (IC's) |

| Mfr | AMD Xilinx |

| Searje | Virtex® UltraScale™ |

|

| Doaze |

| Standard Pakket | 1 |

| Produkt Status | Aktyf |

| Oantal LABs / CLBs | 316620 |

| Oantal logyske eleminten / sellen | 5540850 |

| Totaal RAM Bits | 90726400 |

| Oantal I / O | 1456 |

| Voltage - Oanbod | 0.922V ~ 0.979V |

| Mounting Type | Surface Mount |

| Operating Temperatuer | -40°C ~ 100°C (TJ) |

| Pakket / saak | 2892-BBGA, FCBGA |

| Supplier Device Package | 2892-FCBGA (55×55) |

| Base Product Number | XCVU440 |

FPGA's brûke as ferkearsprozessors foar netwurkfeiligens

Ferkear nei en fan feiligens apparaten (brânmuorre) wurdt fersifere op meardere nivo, en L2 fersifering / ûntsiferje (MACSec) wurdt ferwurke by de keppeling laach (L2) netwurk knopen (switches en routers).Ferwurkjen bûten de L2 (MAC-laach) omfettet typysk djipper parsing, L3-tunnel-ûntsifering (IPSec), en fersifere SSL-ferkear mei TCP/UDP-ferkear.Pakketferwurking omfettet it parsearjen en klassifikaasje fan ynkommende pakketten en it ferwurkjen fan grutte ferkearsvoluminten (1-20M) mei hege trochfier (25-400Gb / s).

Fanwegen it grutte oantal ferplichte komputerboarnen (kearnen), kinne NPU's brûkt wurde foar pakketferwurking mei relatyf hegere snelheid, mar lege latency, skaalbere ferkearsferwurking mei hege prestaasjes is net mooglik, om't ferkear ferwurke wurdt mei MIPS / RISC-kearnen en it plannen fan sokke kearnen basearre op harren beskikberens is dreech.It gebrûk fan FPGA-basearre feiligensapparatuer kin dizze beheiningen fan CPU- en NPU-basearre arsjitektuer effektyf eliminearje.

Befeiligingsferwurking op applikaasjenivo yn FPGA's

FPGA's binne ideaal foar inline-feiligensferwurking yn firewalls fan folgjende generaasje, om't se mei súkses foldogge oan de needsaak foar hegere prestaasjes, fleksibiliteit en operaasje mei lege latency.Derneist kinne FPGA's ek feiligensfunksjes op applikaasjenivo ymplementearje, dy't komputerboarnen fierder kinne besparje en prestaasjes ferbetterje.

Algemiene foarbylden fan ferwurking fan tapassingsfeiligens yn FPGA's omfetsje

- TTCP offload motor

- Reguliere útdrukking oerienkommende

- Asymmetryske fersifering (PKI) ferwurking

- TLS-ferwurking

Folgjende-generaasje feiligens technologyen mei help fan FPGAs

Tal fan besteande asymmetryske algoritmen binne kwetsber foar kompromissen troch kwantumkomputers.Asymmetryske befeiligingsalgoritmen lykas RSA-2K, RSA-4K, ECC-256, DH, en ECCDH binne it meast beynfloede troch kwantumberekkeningstechniken.Nije ymplemintaasjes fan asymmetryske algoritmen en NIST-standerdisearring wurde ûndersocht.

Aktuele foarstellen foar post-quantum fersifering omfetsje de Ring-on-Error Learning (R-LWE) metoade foar

- Iepenbiere kaai Kryptografy (PKC)

- Digitale hantekeningen

- Key skepping

De foarstelde ymplemintaasje fan publike kaai kryptografy omfettet bepaalde bekende wiskundige operaasjes (TRNG, Gaussian noise sampler, polynomiale tafoeging, binary polynomial quantifier division, multiplikaasje, ensfh.).FPGA IP foar in protte fan dizze algoritmen is beskikber of kin effisjint wurde ymplementearre mei FPGA-boublokken, lykas DSP- en AI-motoren (AIE) yn besteande en folgjende-generaasje Xilinx-apparaten.

Dit wyt papier beskriuwt de ymplemintaasje fan L2-L7 feiligens mei help fan in programmabele arsjitektuer dy't kin wurde ynset foar feiligens fersnelling yn râne / tagong netwurken en folgjende-generaasje firewalls (NGFW) yn bedriuw netwurken.